칩 쌓는 '3D패키징'…100兆시장 선수친 삼성

칩 작게 만드는 초미세공정 한계

'3D 패키징' 고성능·저전력 부각

2028년 780억달러로 시장 커져

TSMC·인텔 등도 앞다퉈 개발

내년 3D 패키징 기술 검증 본격화

12일 반도체업계에 따르면 삼성전자는 내년부터 반도체 패키징 기술인 ‘SAINT(Samsung Advanced INterconnection Technology)’를 활용한 3D 패키징을 본격적으로 선보인다. 패키징은 서로 다른 종류의 칩을 연결해 한 칩처럼 작동하게 하는 공정이다. 3D 패키징은 칩을 수평으로 배치하는 일반 패키징과 달리 수직으로 쌓는 게 특징이다.삼성전자는 임시 데이터 저장소 역할을 하는 S램을 중앙처리장치(CPU) 등 프로세서 위에 쌓는 ‘SAINT-S’의 기술 검증을 완료했다. 내년엔 CPU, 그래픽처리장치(GPU) 등의 프로세서 위에 데이터 저장용 D램을 올리는 ‘SAINT-D’, 애플리케이션프로세서(AP) 같은 프로세서를 위아래로 배치하는 ‘SAINT-L’의 기술 검증을 마칠 계획인 것으로 알려졌다.

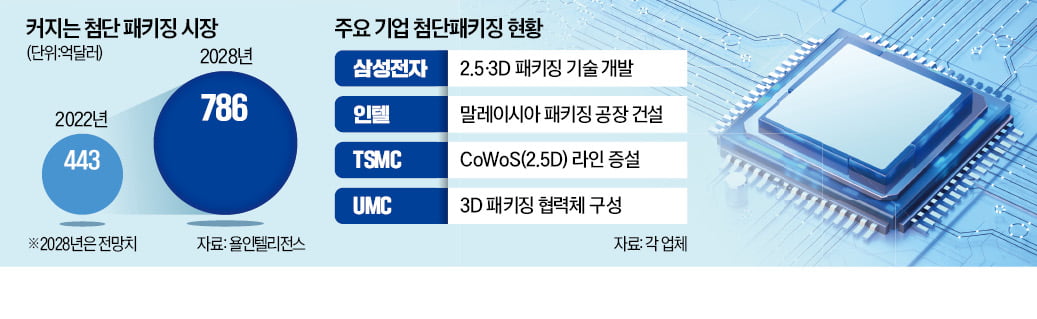

온디바이스 AI용 칩에 활용

삼성전자가 3D 패키징 개발에 주력하는 건 패키징 공정의 중요성이 해마다 커지고 있어서다. 개별 칩을 작게 제조하는 초미세공정 기술의 한계 때문에 반도체 기업들은 만들어진 칩을 잘 배치하고 연결해 성능을 끌어올리는 패키징에 주력하고 있다. 시장조사업체 욜인텔리전스에 따르면 첨단 패키징 시장 규모는 지난해 443억달러에서 2028년 786억달러로 커질 것으로 전망된다.현재는 2.5D 패키징이 첨단 기술로 평가받는다. 2.5D 패키징은 ‘실리콘인터포저’라는 패키징 부품 위에 프로세서와 고대역폭메모리(HBM) 같은 메모리 칩을 수평으로 배치한 것이다. 칩은 실리콘인터포저를 통해 연결된다. 엔비디아의 ‘AI 가속기’는 2.5D 패키징을 통해 제작된다.

3D 패키징은 칩을 위아래로 배치하기 때문에 실리콘인터포저가 불필요하다. 그 대신 TSV(실리콘관통전극) 기술을 통해 칩들이 직접 연결된다. 칩들을 옆으로 이어 붙일 필요가 없기 때문에 공간 활용도가 높아지고 직접 연결을 통해 데이터 처리 속도와 전력 효율을 높일 수 있다.

3D 패키징 수요는 생성형 AI, 온디바이스 AI 등에 적용되는 최첨단 반도체를 중심으로 생겨나고 있다. 삼성전자는 SAINT 기술을 통해 AI 데이터센터용 반도체, 온디바이스 AI 기능을 갖춘 스마트폰용 AP의 성능을 끌어올리는 데 활용할 계획인 것으로 알려졌다.

3D 패키징은 경쟁력 척도

TSMC, UMC, 인텔 등 삼성전자 경쟁사들도 첨단 패키징 기술·서비스 출시에 적극적이다. 대만 TSMC는 3D 패키징 서비스인 ‘SoIC’를 애플, 엔비디아 등 칩 생산에 제공하는 것으로 알려졌다. 인텔도 ‘포베로스’라는 3D 패키징 기술을 자사 최신 칩 양산에 활용하고 있다.이달 초 대만 UMC는 자국 메모리반도체 기업 윈본드, 패키징 1위 업체 ASE 등과 함께 3D 패키징 협업 프로젝트를 가동했다. 반도체업계 관계자는 “첨단 패키징 기술력이 경쟁력의 척도가 되고 있다”며 “한국도 패키징 생태계를 강화하는 데 힘써야 한다”고 강조했다.

황정수 기자 hjs@hankyung.com

-

기사 스크랩

-

공유

-

프린트

!["한국 1인당 국민소득 9000만원"…'장밋빛 전망' 나왔다 [김익환의 컴퍼니워치]](https://img.hankyung.com/photo/202311/02.33347430.3.jpg)

![월가 "인텔 망가졌다"…구글 9년 만에 최고의 날 [글로벌마켓 A/S]](https://timg.hankyung.com/t/560x0/photo/202404/B20240427071917087.jpg)