삼성 숙적 TSMC, 반도체 패키징 협업 위해 일본행

세계 1위 日 이비덴과 협력

삼성전자, 신기술 개발 전력투구

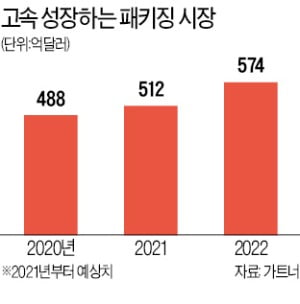

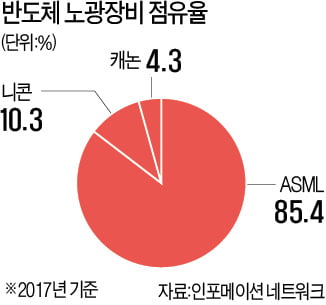

18일 업계에 따르면 파운드리(반도체 수탁생산) 미세화 공정에 이어 반도체 패키징 공정에서 글로벌 경쟁이 격화되고 있다. 기업들은 차세대 패키징 기술에 투자를 늘리고, 다른 업체와의 합종연횡도 마다하지 않는다. 전문가들 사이에선 “향후 10년 뒤에는 패키징 기술력에 따라 반도체 업계 순위가 정해질 것”이라는 전망까지 나온다. 미세화 공정이 물리적인 한계에 부딪힌 상황에서 제품을 차별화할 방법은 패키징뿐이라는 설명이다.

반도체 후공정 중 하나인 패키징 관련 기술이 시장의 주목을 받은 것은 2016년부터다. 삼성전자가 패키징 문제로 애플의 애플리케이션프로세서(AP) 파운드리 수주를 TSMC에 뺏겼다는 소식이 알려지면서 세간의 관심이 집중됐다. 당시 TSMC는 FO-WLP(팬아웃 웨이퍼레벨 패키지) 기술을 개발해 칩 두께는 20% 줄이고, 속도는 20% 높이는 데 성공했다.

글로벌 전문 업체들과 견줘도 세계 3~4위에 들 정도의 패키징 기술력을 갖춘 TSMC가 일본과 손을 잡는 이유는 패키징이 갈수록 복잡해지고 있어서다. 낸드플래시를 쌓듯 칩을 적층하는 기술(TSV), 여러 칩을 조합해 하나의 패키지로 묶는 기술(SiP) 등이 속속 등장하고 있다. 전장과 첨단 서버용 반도체는 패키지 완제품의 면적이 넓기 때문에 크기를 줄이는 데 특화된 FO-WLP로는 한계가 있다.

업계에선 TSMC가 이비덴의 주력 분야인 FC-BGA(플립칩 볼그레이드어레이)를 통해 이 문제를 해결하려는 것으로 보고 있다. 칩을 선이 아닌 면 단위로 기판에 연결하는 기술로, 대면적 패키징에 유리하다. TSMC는 200억엔(약 2100억원)을 투자해 후공정 분야 연구개발(R&D) 센터를 설립하고, 도쿄대에 R&D센터 건립도 추진 중이다.

‘TSMC-이비덴 동맹’에 맞서 삼성전자도 반격에 나섰다. 패키징 경쟁력 강화에 나선 삼성전기는 TSMC의 FO-WLP 기술에 대항하는 PLP(패널레벨패키지) 개발에 착수해 2018년 양산에 성공했다. 수율도 95%를 넘었다. 반도체 패키지 기판을 쓰지 않고 메인보드에 바로 칩을 연결할 수 있는 기술이다.

삼성전기는 이비덴과 대등한 경쟁을 하기 위해 그동안 주력이었던 모바일·PC용 반도체 패키지 기판 외에 서버용 시장에도 뛰어들 방침이다. 업계에서는 올해 삼성전기의 반도체 패키지 기판 매출이 전년 대비 19% 증가한 1조4400억원에 달할 것으로 보고 있다. 삼성전자도 서로 다른 칩을 수직 적층한 ‘엑스큐브’, 여러 칩을 하나의 패키지로 구현한‘아이큐브4’ 등 다양한 신기술을 속속 내놓고 있다.

이수빈 기자 lsb@hankyung.com

-

기사 스크랩

-

공유

-

프린트

![[포토] 삼성전자 '더 세리프 TV' 65형 출시](https://img.hankyung.com/photo/202107/AA.26970645.3.jpg)

![구글, 사상 첫 배당 '주당 20센트'…AI 불안감 덮었다 [글로벌마켓 A/S]](https://timg.hankyung.com/t/560x0/photo/202404/B20240426073327760.jpg)