삼성 vs TSMC, 명운 건 '파운드리 3nm' 경쟁

삼성, 신기술 적용 승부수

"수율 완벽 수준까지 올라와"

TSMC, 6개월 뒤늦게 양산

수율 안정적, 첫 고객 애플 추정

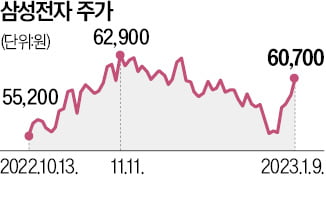

9일 반도체업계에 따르면 삼성전자는 지난해 가동을 시작한 3㎚ 1세대 공정의 수율을 상당 수준까지 끌어올린 것으로 알려졌다. 삼성전자는 지난해 6월 말 세계 최초로 3㎚ 공정에서 칩을 생산, 중국 팹리스(반도체 설계전문 업체)에 전달했다. 당시 수율이 10%란 루머가 돌았다. 이에 대해 업계 고위 관계자는 “현재 삼성 3㎚ 1세대 공정의 수율은 완벽한 수준까지 올라왔다”며 “3㎚ 2세대 공정도 차질 없이 개발 중”이라고 설명했다.

삼성전자는 3㎚ 공정부터 GAA(gate-all-around) 구조를 적용했다. GAA는 전류가 흐르는 채널 4개 면을 게이트가 둘러싸는 형태의 구조다. 채널의 3개 면을 감싸는 기존 핀펫(Fin-FET) 구조 대비 칩의 전력 효율성과 성능이 뛰어나다.

3㎚ 같은 최첨단 공정에 신기술을 적용하는 것은 ‘도박’에 가까운 승부수로 평가된다. 초기 수율을 잡는 데 어려움을 겪을 수 있어서다. 삼성전자는 오랜 준비를 통해 과도기를 최소화했다.

TSMC는 3㎚ 칩 양산 시점이 삼성전자에 비해 6개월 정도 늦었다. 지난달 29일에야 대만 남부 타이난과학단지 내 18팹에서 3㎚ 양산 행사를 열었다. TSMC는 핀펫 기술을 유지하며 3㎚ 공정을 개발했다. 첫 고객은 애플인 것으로 추정된다.

TSMC의 3㎚ 공정 수율은 신기술을 적용한 삼성전자보다 안정적인 것으로 알려졌다. 대만 언론들은 ‘수율이 최대 85%’라고 보도하고 있다. 국내 반도체업계 관계자는 “주요 고객사인 애플의 칩 출시 일정과 TSMC의 3㎚ 양산 시점을 감안할 때 TSMC의 80~85% 수율은 과장된 수치”라며 “높아야 50% 수준”이라고 분석했다.

업계에선 올해 3㎚ 공정 고객 확보 경쟁이 뜨거워질 것이란 전망이 나온다. 2㎚, 1㎚ 등으로 선폭(회로의 폭)을 좁히는 게 점점 더 어려워지고 있어 3㎚ 공정이 2~3년 동안 파운드리 시장의 핵심 공정 역할을 할 것으로 예상되기 때문이다. 시장조사업체 옴디아는 2025년 3㎚ 공정 시장 규모가 254억5000만달러(약 31조6400억원)를 기록, 5㎚(192억700만달러)를 압도할 것으로 봤다.

TSMC가 미국 애리조나주에 추가로 짓기로 한 파운드리 공장에도 3㎚ 공정이 구축된다. 퀄컴, AMD, 엔비디아 등 주요 팹리스도 삼성전자, TSMC 등 파운드리업체들과 함께 3㎚ 공정용 칩 개발을 본격 논의하기 시작했다.

황정수 기자 hjs@hankyung.com

-

기사 스크랩

-

공유

-

프린트

![서학개미 뒤집어졌다…다우지수 종가기준 첫 4만선 돌파 [뉴욕증시 브리핑]](https://timg.hankyung.com/t/560x0/photo/202405/AD.36579999.1.jpg)