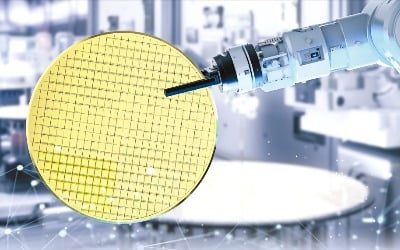

"이제 메모리 초격차는 SK하이닉스"…'세계 최고층' 238단 낸드 개발

내년 상반기 양산…최고층·최소 면적

생산성·속도·전력소모 획기적 개선

![SK하이닉스가 개발한 238단 4D 낸드 [사진=SK하이닉스]](https://img.hankyung.com/photo/202208/01.30812444.1.jpg)

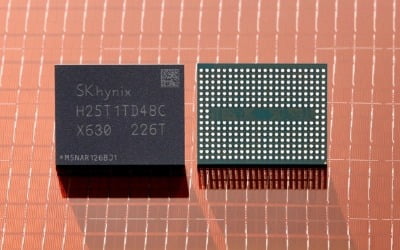

SK하이닉스는 최근 238단 512Gb(기가비트) TLC(Triple Level Cell) 4D 낸드플래시 샘플을 고객에게 출시했고 내년 상반기 양산에 들어간다는 계획이다.

낸드플래시는 한 개의 셀(Cell)에 몇 개의 정보(비트 단위)를 저장하느냐에 따라 △SLC(Single Level Cell·1개) △MLC(Multi Level Cell·2개) △TLC(Triple Level Cell·3개) △QLC(Quadruple Level Cell·4개) △PLC(Penta Level Cell·5개) 등으로 규격이 나뉜다. 정보 저장량이 늘어날수록 같은 면적에 더 많은 데이터를 저장할 수 있다.

회사 측은 "2020년 12월 176단 낸드를 개발한 지 1년7개월 만에 차세대 기술 개발에 성공했다"며 "특히 이번 238단 낸드플래시는 최고층이면서도 세계에서 가장 작은 크기의 제품으로 구현됐다"고 강조했다.

SK하이닉스는 이날 미국 산타클라라에서 개막한 '플래시 메모리 서밋 2022'(FMS)에서 신제품을 공개했다. FMS는 매년 미국 캘리포니아 주 산타클라라에서 열리는 낸드플래시 업계 세계 최대 규모 콘퍼런스로, 올해 행사 기조연설에서 SK하이닉스는 낸드 솔루션 자회사인 솔리다임(Solidigm)과 함께 공동 발표했다.

행사 기조연설자로 나선 최정달 SK하이닉스 부사장(낸드 개발담당)은 "4D 낸드 기술력을 바탕으로 개발한 238단을 통해 원가, 성능, 품질 측면에서 글로벌 톱클래스 경쟁력을 확보했다"며 "앞으로도 기술 한계를 돌파하기 위해 혁신을 거듭해 나갈 것"이라고 강조했다.

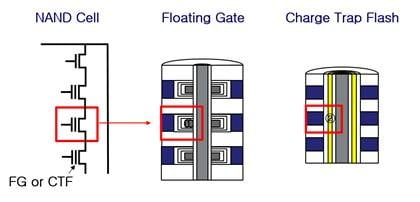

CTF는 전하를 도체에 저장하는 플로팅 게이트(Floating Gate)와 달리 전하를 부도체에 저장해 셀간 간섭 문제를 해결한 기술로, 플로팅게이트 기술보다 단위당 셀 면적을 줄이면서도 읽기, 쓰기 성능을 높일 수 있는 것이 특징이다.

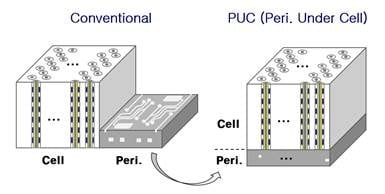

PUC는 주변부 회로를 셀 회로 하단부에 배치해 생산효율을 극대화하는 기술이다. 특히 4D는 3D 대비 단위당 셀 면적이 줄어들면서도 생산효율은 높아지는 장점을 가진다.

이번 238단은 단수가 높아진 것은 물론 세계 최소 사이즈로 만들어져 이전 세대인 176단 대비 생산성이 34% 높아졌다. 이전보다 단위 면적당 용량이 커진 칩이 웨이퍼당 더 많은 개수로 생산되서다.

238단의 데이터 전송 속도는 초당 2.4Gb로 이전 세대 대비 50% 빨라졌다. 또 칩이 데이터를 읽을 때 쓰는 에너지 사용량이 21% 줄어 전력소모 절감을 통해 ESG 측면에서 성과를 냈다고 SK하이닉스는 강조했다.

SK하이닉스는 PC 저장장치 cSSD(client SSD)에 들어가는 238단 제품을 먼저 공급하고 이후 스마트폰용 및 서버용 고용량 SSD 등으로 제품 활용 범위를 넓혀나가기로 했다. 내년에는 현재의 512Gb보다 용량을 2배 높인 1Tb 제품도 선보일 예정이다.

강경주 한경닷컴 기자 qurasoha@hankyung.com

-

기사 스크랩

-

공유

-

프린트

![기업실적 호조에 일제히 상승…테슬라는 최대폭 매출 감소[뉴욕증시 브리핑]](https://timg.hankyung.com/t/560x0/photo/202404/ZA.36457219.1.jpg)

![[단독]하이브 키운 '멀티 레이블'이 제 발등 찍었다](https://timg.hankyung.com/t/560x0/photo/202404/02.33877838.1.jpg)