삼성 보고있나…TSMC, 3나노 생산시설 늘려 독주 굳힌다

로이터 "3나노 라인 1개당 28조 들어"

3나노, 파운드리 초미세공정 경쟁 분수령

'압도적 점유율' TSMC, 독주체제 굳히기

삼성, 차별화 기술로 3나노서 격차 줄이기

TSMC 점유율 56%, 삼성 18% '2배' 차이

반면 5나노 공정 양산에서 TSMC에 뒤졌던 삼성전자는 내년 하반기 3나노 반도체를 먼저 양산해 격차를 줄이겠다는 계획이다.

18일 관련 업계에 따르면 TSMC는 미국에 수십조원을 추가로 투자해 3나노 이하 최첨단 반도체 생산 라인을 구축할 계획을 세우고 있다. 현재 TSMC는 120억달러(약 14조원)를 투자해 미국 애리조나주 피닉스에 5나노 공정의 생산 라인을 증설하고 있는데 여기에 추가로 3나노 이하 최첨단 공정을 갖춘 생산 라인을 5개 증설해 총 6개의 신규 생산 라인을 구축할 계획이다.

로이터통신은 "3나노 생산 라인 하나를 구축하는 데만 최대 250억달러(약 28조원)가 든다"고 했다. 앞서 TSMC는 지난달 1일 "향후 3년간 미국 생산 라인 증설에 1000억달러(약 110조원)를 투자하겠다"고 밝혔다. 여기에 3나노 공정까지 미국에 만들면 상당한 규모의 추가 투자가 이뤄지는 셈이다.

반도체 업계에선 누가 먼저 3나노 양산을 시작하는지에 따라 초미세공정 경쟁의 분수령이 될 것으로 본다. 반도체는 나노 단위인 회로의 선폭이 좁을수록 저전력·고효율 칩을 만들 수 있다. 5나노도 머리카락 굵기(0.1㎜)의 5만분의 1에 불과할 정도로 미세하지만 3나노는 이보다 더 작다. 3나노 공정으로 제작된 반도체는 5나노 대비 칩 면적은 35% 줄이면서, 성능과 배터리 효율은 각각 15%와 30% 올릴 수 있는 것으로 알려져 있다.

삼성전자는 고객사들에 3나노 공정의 기술차이를 어필하고 있는 것으로 알려졌다. 삼성전자는 3나노 공정에서 TSMC와 달리 전통적인 방식의 핀펫(FinFET)이 아닌 GAA(Gate All Around) 기술을 적용한다. 핀펫은 초미세공정에서 다소 불리한 기술로 알려져 삼성전자가 GAA를 적용해 양산에 성공한다면 TSMC보다 유리한 고지에 오를 수 있다고 업계는 보고 있다. 반도체 업계 한 관계자는 "다만 과거 삼성이 낸드플래시 생산에서 비용을 줄이기 위해 '원스택(one-stack)' 기술을 시도했다가 실패한 뒤 '더블스택'으로 바꿔 미국 마이크론 같은 회사들이 쫓아올 수 있는 빌미를 만들어줬던 것처럼 이번에도 비슷한 위험을 안고 가는 것"이라고 했다.

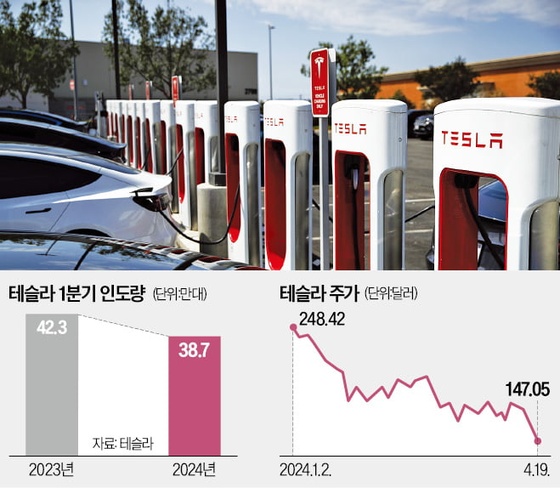

현재 초미세 공정 영역으로 평가받는 7나노 이하 반도체 양산이 가능한 업체는 전 세계에서 TSMC와 삼성전자뿐이다. 두 회사 모두 현재 5나노 제품을 양산하고 있는데 TSMC가 약 6개월 앞선다는 평가를 받는다. 이 때문에 6개월 마다 신제품을 출시하는 글로벌 고객사들이 TSMC 제품을 더 선호하고, 이것이 두 회사의 점유율 격차가 쉽게 줄지 않는 이유로 꼽힌다. 시장조사업체 트렌드포스에 따르면 지난 1분기 TSMC의 파운드리 점유율은 56%로, 2년 전 같은 기간보다 8%포인트 늘었다. 반면 삼성전자의 1분기 점유율은 18%로 소폭 줄었다.

노정동 한경닷컴 기자 dong2@hankyung.com

-

기사 스크랩

-

공유

-

프린트

!['베니스의 장인들' 르네상스 조선소에 쿵쿵쿵 망치질! 클래스가 달랐던 토즈 전시 [2024 베네치아 비엔날레]](https://timg.hankyung.com/t/560x0/photo/202404/01.36496137.3.jpg)