입력2006.04.02 14:49

수정2006.04.02 14:53

삼성전자는 28일 비메모리반도체에서 회로선폭 90나노 공정기술을 개발하는데 성공했다고 발표했다.

나노(nm·10억분의 1m)급 기술은 현재의 마이크로미터(㎛·1백만분의 1m)급 기술보다 한차원 높은 수준의 기술로 반도체업계에서는 업계 1위인 인텔과 대만의 파운드리(수탁가공생산)업체 TSMC에 이어 세번째로 개발됐다.

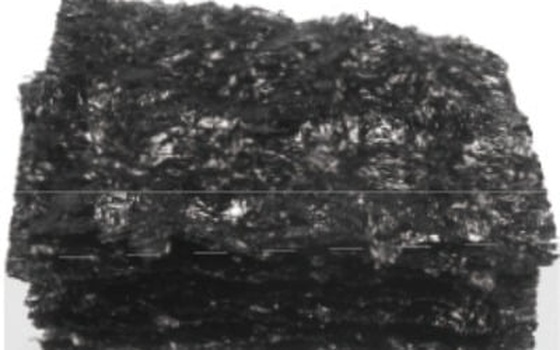

삼성전자의 나노공정기술은 1.0V의 저전압에서 동작하는 90nm 크기의 미세한 트랜지스터에 구리 다층배선공정을 적용한 것으로 △1.6nm의 초박막 게이트 절연막 형성기술 △70nm 게이트 폭의 초미세 트랜지스터 형성기술 △저에너지 주입기술 △초정밀 사진식각 기술을 이용한 구리 다층배선 공정기술 등이 새로 개발됐다.

0.13㎛ 공정과 비교하면 동작속도는 30% 향상되는 반면 칩 면적은 50% 줄일 수 있어 그만큼 원가경쟁력이 높아지게 된다.

특히 여러가지 반도체칩을 하나의 칩으로 집적시키는 차세대반도체 SOC(시스템온칩)개발에 크게 기여할 전망이다.

삼성전자는 이번 기술을 2004년부터 미래 주력사업인 휴대기기용 CPU(중앙처리장치) 및 SOC제품 양산에 우선 적용하고 ASIC(주문형반도체) 마이크로프로세서 모바일칩 내장형메모리(임베디드메모리) 및 소비자제품용 IC 등 비메모리 전분야로 확대할 예정이다.

그동안 메모리반도체에서는 0.15㎛공정기술이 주로 적용되고 있으며 삼성전자는 0.10㎛(1백nm)급 기술까지 개발했었다.

대우증권의 전병서 리서치본부장은 "삼성전자는 그동안 1기가D램 개발 등을 비롯해 각종 기술개발에서 여타 업체보다 2∼3년가량 앞섰다"면서 "이번 나노급 기술개발은 이를 확인시켜준 것"이라고 설명했다.

김성택 기자 idntt@hankyung.com